# If it moves, simulate it!

## Andrew Neureuther\* EECS, UC Berkeley, 205 Cory Hall 31772, Berkeley, CA 94720-1772 \*neureuth@eecs.berkeley.edu; phone 1 510-642-4590; fax 1 510 642-2739

### ABSTRACT

In the last 35 years modeling of projection printing has undergone many paradigm shifts in physical models, computational engines, algorithms and opportunities. The trigger event for the first quantitative positive resist Dill model was the development and application of automated thin-film measurement equipment. The use of partial coherence which helps imaging also complicates the understanding and necessitates the use of simulation to guide lithography practice. Simulation has also played an important role in discovery (intensity imbalance in phase-shifting masks), invention (self-interferometric mask monitors) and creation of analysis techniques (first-cut accurate fast-CAD). The current challenges and growth areas for simulation include calibration, synergy with metrology, electronic self-testing and linking circuit design and fabrication.

Keywords: modeling, simulation, resist, image, electromagnetic, illumination, partial coherence, profile evolution, defect, monitor, interferometric

## 1. INTRODUCTION

Lithography modeling of Integrated Circuit manufacturing developed much the same way that machine tooling developed in that the advances of one generation helped established the advances of the next generation. It is not hard to be successful in computer simulation when among those advances is a 40 million fold decrease in the cost of computation. Yet the depth of sophistication in physical models required by the semiconductor industry has pushed technology into unknown frontiers of need based science that require huge simulation efforts. Similarly, the requirements for the design evaluation and pre-compensation of billions of details in a full chip layout have pushed the needs for entirely new strategies in physical models and computational algorithms.

The history of lithography simulation has yet to be distilled and given the hundreds of contributors and continuing growth of the field, there are far too many events to capture in a balanced perspective. Rick Dill [1] gave a history of the cornerstone development of the 'Dill' papers from 1975 [2-5]. Chris Mack has also provided a historical view associated with the development of Prolith [6]. The goal of his paper is to look back at the evolution of lithography modeling work from my involvement with Rick Dill at IBM and the experience in our university research group afterward to gain a historical perspective and then annotate it with personal experiences. These experiences are really a tribute both to the creativity, excitement and drive of the students and to the technologists who asked leading question that motivated and focus our contribution. The title of this paper reflects the view of the challenge to our research group that if a concern looked important or was about to 'move' that we should 'simulate it'. There were many, many contributions and my apologies for selecting just a few for illustration here. Also, my apologies if the viewpoint of our experience in academic work is a bit myopic to the reader.

The paper begins in Section 2 with an overview of the trigger event for lithography modeling, the rapid growth since in required physical phenomena, and the interaction of modeling with production. Stepper manufacturers introduced restricted illumination in the very first tools that produces partial coherence with distance across the mask. Section 3 shows how this partial coherence helps imaging but also how it complicates both the practice and modeling of lithography. Section 4 describes how simulation has been used to establish 'back-of-the-envelope' lithography models that are as important in lithography practice as the simulation capability itself. The rapid evolution of hardware, infrastructure and algorithms and how it spawned many branching directions is discussed in section 5. Sections 6 and 7 describe current challenges and future growth areas for simulation.

## 2. TRIGGER EVENT AND EVOLUTION OF SIMULATION

About 1970 there were signs of a major change in lithography for semiconductor manufacturing. Many types of thinfilms were in use and automated thin-film measurement equipment was needed for rapid production monitoring of both thicknesses and qualities. Production busts had occurred and had been traced to subtle changes in resist resins and/or exposure source aging. Positive resists were becoming available, had less bridging and better resolution. Infact, Janos Havas of IBM demonstrated, they were even able to produce fringes on line-edge profiles due to standing waves from substrate reflections. Projection printing was also being explored by the group of Yanus Wilczynski in IBM.

At this point Rick Dill of IBM under took a key initiative in automated thin-film measurements. He had a love for thinfilms and optics and it was also necessary to re-tool his Germanium pilot line activities. Rick decided to re-organize his group to develop automated thin-film ellipsometer and spectrometer measurement equipment in support of manufacturing. These tools were soon extended for measurement of resist bleaching and thickness during development. The goal was to automate the measurement process so that a characterization experiment that took a person month could be done in minutes. The use of optically matched substrates at the exposure wavelength facilitated exposure bleaching. The mismatch of optical properties at wavelengths other than the exposure wavelength with the speed of the automated spectrometer made measurement of the remaining resist thickness nearly instantaneous. Karl Konnerth and Pete Hauge developed the automated tools. Bill Hornberger and Jane Shaw provided a control by making interrupted resist dissolution measurements by hand. Jim Tuttle found the thin-film mathematics for energy deposited in the resist and had interest in the optics and dissolution. Ed Walker of post-exposure bake fame provided images printed in resist for comparison.

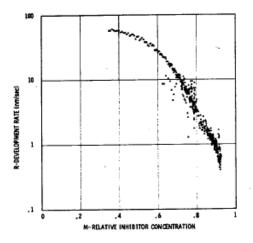

The most important outcome from this new capability was the determination that resist could be modeled as a surface etching phenomena with an etch rate that depended on the state of the photochemistry and not the manner in which the exposure was delivered [3,4]. The key evidence was that the dissolution rate at the bottom of a highly exposed sample was the same as that at the top of a lightly exposed sample provided that the doses were adjusted to produce the same chemical state. This was show by first calculating the chemical state, termed M, from and exposure bleaching model using the bleachable absorption A, unbleachable absorption B and bleach rate C from the equations in Figure 1. The dissolution rate could then be plotted versus M. The original data from reference [3] is shown in Figure 1 and the overlapping data from multiple exposure levels tends to produce a single valued curve. Since the initial plot was on semi-log paper and was parabolic in shape, three parabolic fitting parameters (E values) described the dissolution rate R(M) as an exponential quadratic in M. The ABC's together with the three E's comprised the so called Dill model that described both exposure and dissolution. This modeling breakthrough was a major step in converting the 'art of lithography' into the quantitative 'science of lithography' that we know today.

Fig. 1. Bleaching equations and development rate curve for AZ1350J photoresist in 1:1 AZ developed:  $H_20$  at  $20^{\circ}C$  (70°C prebake) from [3] and modeling equations.

Once the exposure and dissolution model had been established it was possible to simulate the time-evolution of resist profiles in projection printing [5]. The simulation code was written during 1972 in IBM's APL engineering language using a Selectric typewriter with a special character ball with mathematical symbols. APL had shift operators and they

were convenient for finding the resist surface and number of adjacent elements exposed to development in a cell removal algorithm. Because dissolution rates varied by over a factor of 200 an adaptive time step and over/under etching of cells was included to speed up the code. The code itself ran on the mainframe. The simulation process began by first coding and an iterative bleaching process that included standing waves and allowed the optical properties of the resist to change dynamically with each small exposure increment leading to the largest possible exposure and thus create M(E,z). A simple imaging model was then used to create an image I(x) normalized to clear field. With the exposure dose this image gave the local relative exposure dose at a horizontal point. For the 0.28 NA lenses, the local relative exposure was assumed to propagate vertically in the resist as if the problem was horizontally uniform and 1D. This enabled the chemical state as a function of depth and horizontal distance M(x,z) to be built from columns of M(E,z). The dissolution rate R(M) function was then used to convert M(x,z) to R(x,z). Finally, the time-evolution of the resist profile was modeled by the cell removal algorithm for the development time specified.

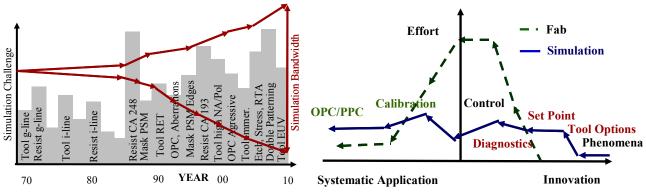

In the 35 years since the Dill model was developed the scope of the physical effects included in lithography modeling has experienced enormous growth. Figure 2 shows how the physical phenomena important in modeling projection printing have grown with time. The models first progressed from g-line, to 2D images, new materials and issues such as filter leakage at i-line. DUV resists, Resolution Enhancement Techniques (RET) based on off-axis illumination and Phase-Shifting Masks (PSM) came in the mid 80's. Optical Proximity Correction (OPC) consisting of pre-compensation of the entire chip layout occurred in the mid-90's with a new class of algorithms. Second order effects of aberrations in lens, mask edge effects, high-NA and polarization occurred in the late 90's. Process Proximity Correction (PPC) and Aggressive OPC as well as 193 nm resists became necessary in the late 90's. More recently immersion and non-lithography effects of etch, stress, and rapid thermal anneal have required modeling. The industry is now facing double and/or spacer patterning and re-calibration for the unique characteristics of EUV. This rapid rise in the physics has required a corresponding rise in level of effort indicated in Figure 2 as the simulation bandwidth.

Fig. 3. Simulation contributes in many phases of a technology node in moving from innovation through systematic application.

Lithography modeling has managed to pay for itself. Before turning to just how simulation contributes it is interesting to first examine the time-line for production at a technology node. The dotted line in Figure 3 is a rough sketch of the level of effort in developing and operating a fabrication facility from the time of innovation to systematic application. The manufacturing capability comes into existence with the availability of alpha tools and ramps very quickly to establish a working process with monitoring and control. Further effort is needed to improve the yield and to improve the electrical accuracy of the design interface. The effort then drops off as attention turns to newer facilities.

The solid line in Figure 3 compares the lithography modeling and simulation contributions to the stages of developing manufacturing. Very early on the time-horizon is the simulation of phenomena which might be considered to be 'weird and esoteric' and usually do not pay for themselves directly. Nonetheless they play an important role in guiding technology innovation decisions. A few years prior to building new production facilities manufactures are more than willing to pay for hypothetical studies of potential new equipment capabilities to determine their specifications for production tooling. Operation issues then ensue that also pay for themselves including determining the set point, tool performance diagnostics, monitoring and control. A major new value added proposition of pre-compensation of full layouts with OPC and PPC then arises and is paid for out of the design budget. Success in pre-compensation of course is dependent on calibrating the models to guarantee that an IC Design will work.

#### 3. PARTIAL COHERENCE: HELP AND HEADACHES

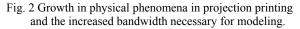

In a Kodak Microelectronics conference in Monterey in 1973, a major discussion ensued on how Modulation Transfer Function (MTF) curves for lenses showed that it should be quite reasonable to move to smaller feature sizes with a given lens. The MTF is the amplitude transfer for a sinusoidal intensity component of an incoherent intensity distribution at the mask plane. A typical MTF curve is labeled 'sinusoidal object' in Figure 4. Looking at this curve and imagining tighter control in manufacturing it seems quite reasonable to move down the MTF curve from the 60% modulation point to the 40% modulation point. This would certainly be the case for photography where it is safe to assume that the light from each point or pixel on the object is incoherent with the light from every other pixel. In such a case images can be computed from the intensity at the mask alone by a linear transform process. This consists of taking the Fourier transform the intensity from the object, then weight each spatial frequency component passing through the lens by its MTF and finally taking the inverse Fourier transform.

Fig. 4. MTF and contrast versus normalized spatial frequency passing through the lens. As s decreases from unity the contrast increases and more importantly the image value just inside the masked area is much lower.

What was not well known to the lithographers, however, was that stepper manufacturers were improving their imaging quality by limiting the illumination to under fill the entrance pupil of the lens. In the simplest case this consisted of restricting the cone of illuminating light such that the lens pupil was only filled to a relative radius of sigma (typically 0.3 to 0.7). This angular illumination restriction introduced partial coherence of overlapping electric fields from adjacent pixels on the mask. This in turn required new computational procedures based on the Fourier transform of electric fields, passing them though the lens, and finally taking the time-average of all electric fields at the wafer to evaluate their degree of partial coherence.

The image intensity versus horizontal position in Figure 4 shows that the associated image improvement was phenomenal. The edge slope increased, the line edge value dropped from 0.5 to 0.25 and most importantly that the toe value just inside the dark region dropped to nearly zero. This greatly improved the relative slope known today as the normalized intensity log slope (NILS). An approximate way to characterize the improvement with partial coherence is to consider an equal line and space pattern and plot the image contrast consisting of the ratio of the image max-min over max+min. The contrast curves labeled  $\sigma$  of 0.3 and 0.7 in Figure 4 show that the image contrast (even with some defocus) is near 100% at the spatial frequency corresponding to 60% MTF. But note that the contrast quickly drops in a cliff like manner to values below 50% in moving to spatial frequencies corresponding to 40% MTF. Worse yet this cliff also shifts to even lower spatial frequencies with more defocus. The technologists who were not aware of the illumination and lens working together as an optical system were convincing themselves to walk off this cliff in contrast versus spatial frequency in moving to smaller feature sizes.

The use of partial coherence, while an improvement in imaging, is a major headache both in the practice and simulation of lithography. The practice of lithography suffers from the fact that the image is no longer a linear addition of images

from various mask openings. This in turn creates the Mask Error Enhancement Factor (MEEF) that approximately doubles and quadruples the tightness of edge placement in mask making for lines and contacts, respectively. In simulation, dealing with partial coherence is probably responsible for 80% of the CPU cycles used in lithography modeling. For example if the imaging were incoherent OPC could be done with a single kernel. Or, better yet, Hopkin's, Abbe's, and OPC methods could be replaced by linear transforms acting on intensity. Today, for low  $k_1$  manufacturing the interplay of high off-axis illumination with the mask pattern and lens still provides additional leverage for further image improvements. But is also an ever increasing challenge for tool design, maintenance, mask making and modeling.

#### 4. SIMULATION BUILDS THE PHYSICAL FOUNDATION

Perhaps as important as the simulation capability is the ability of simulation to guide the development of the physical understanding of which factors dominate lithography practices and to what extent. Systematic simulation studies provide the data from which engineering models of lithography physics are built. In some instances these trends are captured in back-of-the-envelope models. In others, the data have given new insights and even lead to new theoretical results. Often the physical understanding was developed in response to questions from technologist such a Ron Finnella of Hughes, John Kerr of Signetics and Norm Ahlquist of Intel. Early examples of studies include the simulation and experimental dependence of the sign of the proximity effect on the partial coherence factor [7] and simulation studies of phase shifting masks [8].

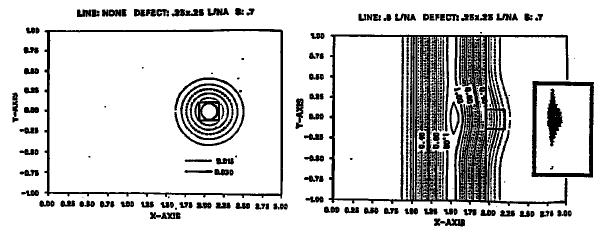

An important example of building a physical foundation through simulation is the study defect interactions with features shown in Figure 5 [9]. A question from Wolfgang Arden of Siemens was why do programmed defects show up so clearly on opaque features especially when they are so small that they barely print. His SEM image of such a layout is shown in the insert in the right hand side of Figure 5. John Skinner of Bell Labs always raised the question of how the defect shape would affect the tendency of the defect to print. Simulation of the image intensity of a transparent isolated 0.25  $\lambda$ /NA by 0.25  $\lambda$ /NA defect and its placement near a transparent 0.8  $\lambda$ /NA line are also shown in Figure 5. The isolated defect has a peak intensity of only about 3% of the clear field. The defect adjacent to the feature causes an increase in intensity of 17% of the clear field. Since 0.17 is close to sqrt(0.03) and I = EE\*, one immediate clue is that the electric field from the defect is directly adding to the electric field of the feature to produce a significant 12% linewidth change. Further simulation characterization [10] has established algebraic models in which the width of the resist image is proportional to the area of the defect and the height of the defect is given by the 1.2  $\lambda$ /NA spot size of the exposure tool.

Fig. 5. The SEM insert on the right hand side shows the printed image of a programmed defect in positive resist. The left side show the image of a 0.25 by 0.25  $\lambda$ /NA defect and it produces only 3% of the clear field intensity. The right side shows how this same defect adjacent to a 0.8 $\lambda$ /NA line and it produces a 17% clear field intensity along the line edge.

Another example of building a physical foundation from image simulation is the simulation study published by Wantanabe [11] of the darkness beneath a phase defects as a function of focus. The relative severity factor of a phase defect compared to an opaque defect in focus is  $[1-M\cos(\phi_D)]$  where  $\phi_D$  is the phase of the defect[8]. The worst case is for a defect that transmits fully with 180° phase. The key finding from the Wantanabe study was that the 90° defect produces an asymmetrical response through focus with its lowest minimum intensity when out of focus. This simulation

characterization revealed an important consequence namely that in inspecting for the presence of phase defects it is necessary to inspect at more than one focal position. The physical explanation is that the small defect scatters light across the pupil taking a uniformly weighted average of defocus optical path difference (OPD) over the full pupil of the lens while the clear field signal only takes an average weighted closer to the center of the pupil where the OPD for focus is smaller. The severity factor is thus generalized to  $[1-M\cos(\phi_D+\phi_{PUPIL}(f)]]$  where  $\phi_{PUPIL}(f)$  represents the difference in the average phase added to the defect relative to the clear field and is proportional to the defocus distance f.

Building credibility for simulation was not an easy job. In the early days doubts about the value of simulation were often openly expressed in questions at conferences. About 1978, a prominent experimentalist bluntly asked 'Has simulation ever discovered anything first?' This was painful as simulation was still struggling to include all the physics in play and was not trusted to explore new scenarios. Even in the early 80's we were having trouble keeping up with exposure tools and resists. At Berkeley the students working on simulation had put up a sign that read 'Those who can do and those who can't simulate." The students at Stanford had a similar sign that read 'Yesterday's Technology Simulated Tomorrow.'

The seminal event in the discovery of new lithography phenomena through simulation was the identification of the Intensity Imbalance in Phase-Shifting Masks in 1992 by Alfred Wong [12]. In simulations at Berkeley we were looking for methods for checking the accuracy of the thick mask and image simulation. A perfect intensity balance between 0° and 180° openings was one check we were using. After finding a residual Intensity Imbalance with many different numerical tunings we decided that the Intensity Balance was a real physical effect. Sematech suggested collaboration with Bell Labs where Chris Perriot and Sheila Vaidya quickly verified the effect experimentally. In the experiment images printed in a negative resist always produced smaller linewidths for the phase shifted openings.

Electromagnetic simulation of has been a major tool for guiding technology innovation and dealing with thick mask effects. This includes ATT-PSM and contact hole inspection by Robert Socha [13,14], EUV absorber shadowing and buried defects by Tom Pistor[15], 3D dielectric defects [16], buried defects and phase-shifting EUV masks and nanoimprint inspection by Yun-Fei Deng[17] and Plasmon effects by Dan Ceperley [18].

Lithography characterization is not complete without an understanding of how the resist recording media transfers the aerial image into a line-edge profile on the wafer. This is a continual and time consuming pursuit as resist technology evolves and today it also must include modeling line edge roughness (LER). Early work on combining rate and images by Mime O'Toole for positive tone novalak resists showed that reduction in the image toe was more important than the increased slop or high intensity shoulder in the bright area [19]. Deok Kim in measuring resists found that surface rate retardation effects in some resists led to more rectangular resist profiles [20]. More suitable algebraic models for resist dissolution in use today were introduced by Chris Mack [21]. The DUV resists were initially negative tone and FTIR measurements allowed cross-linking models to be developed by Rich Ferguson [22]. Silvlation models were also developed by Chris Spence based on FTIR measurements [23]. For positive DUV resists the exposed area or trench always grew with additional bake time regardless of the feature type and was modeled with exposure enhanced diffusion by Marco Zuniga [24]. But resists showed a very strong propagation front behavior as determined experimentally by Grant Willson's group at AT Austin and Ebo Croffie decided to simulate the generation and collapse of free volume in the resist during post-exposure bake [25]. Surface generation and recombination rates to account for effects at the top surface and substrate as well as buffering of the exposure generated acid as proposed by Seiji Nagahara of NEC were added in 3D as well as LER by Lei Yuan[26]. Much of this work was encouraged by Jim Thackery of Shipley and Greg Wallraff of IBM, among others.

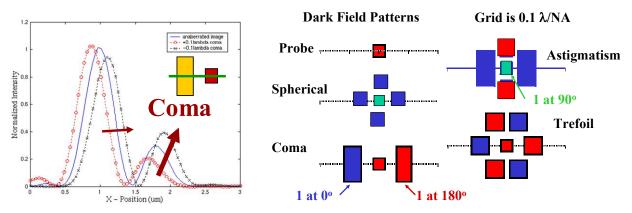

Another important example of the contribution of simulation to understanding of lithography physics was the discovery of self-interferometric Pattern-and-Probe aberration monitors and their theoretical basis [27]. Jim Wiley who was working on mask inspection asked how aberrations would effect the interaction of defects with features. Simulations quickly showed that not much of an additional effect would be observed for typical defects in the presence of small aberrations. But when the defect was super-sized suddenly the defect printed by itself. This is illustrated in Figure 6 where the defect intensity rises sharply with the level of coma. With simulation it was easy to enhance the effect further by adding additional adjacent features with various phases as also shown in Figure 6. The radial phase variation was chosen to follow that of the aberration under study. The knowledge that the fields at the lens and mask plane are related by Fourier transforms then lead to the realization of a new theoretical result. Namely, the worst possible pattern to put on a layout to interplay with a given Zernike aberration is the inverse Fourier transform (IFT) of that Zernike aberration. It was also realized that since the average value of each non-constant Zernike term is zero, the IFT has a zero on axis value that is a fortuitous location for an interferometric 90° or 180° probe to detect even or odd aberrations, respectively.

Fig. 6. A super-sized 180° degree phase defect can reacts strongly to coma and its sigh change (on left). Adding additional features in accordance with the rotational symmetry of the aberration then strengthens the reaction. Note that for even aberrations that the central probe is phased 90° degrees.

The discovery of self-interferometric effects from patterns on photomasks started a research theme we termed 'Phase-Shifting Masks as Precision Instruments.' Initial testing of the pattern-and-probe aberrations monitors worked experimental even in the presence of electromagnetic edge effects and mask making tolerances. In addition to aberrations, it was also found possible to develop mask patterns for monitoring illumination intensity and its polarization [28]. These new cases of monitors enhanced sensitivity were based on a combination of ideas from theory and were calibrated through simulation. We are deeply indebted to Mircea Duse of ASML, Franklin Kalk of Toppan, Chris Progler of Photronics, Jongwook Kye of AMD, and Steve Sloaneker of Nikon for making possible the experimental testing of these self-interferometric monitors in several rounds of experiments.

The viewing of potential lateral interactions at the mask plane soon stimulated another research theme called Pattern Matching for first-cut accurate fast-CAD estimates of process effects [29]. The basic idea was to first identify the physical nature of the lateral spillover of influence among features as the maximal lateral impact function. For a given set of lens aberrations this was, of course the, IFT of the corresponding sum of Zernike's present. The second phase was to scan the entire chip layout with this function to identify the locations with the maximum degree of similarity as evaluated by convolution. These match locations were then exported for further evaluated such as via simulation. Speed was of the essence and since less physics was being done that in OPC programs the metric for success was a code that was much faster than OPC. Frank Gennari shortly produced a very remarkable piece of software called the Pattern Matcher. It used a new data structure for the mask representation, pre-computation of overlap convolutions, adaptive compression for early go-no-go refinement decisions, and leveraged graphics hardware. Running on only a desk top computer Frank was able to read in an entire AMD Opteron chip layout and correctly find all occurrences of a particular problematic pattern in less than 20min. Pattern Matching at the photomask plane is now a commercial EDA tool.

#### 5. ROLE OF HARDWARE, INFRASTRUCTURE AND ALGORITHMS

The advances in computer hardware for lithography modeling have been explosive over the last 35 years. In 1973 the use of a one MIP machine cost \$500/hr. Our research goal was to do a simple image, etch or deposition simulation for less than \$1. VAX machines brought the cost down to \$15 hr and at the same time provided more throughput. The PC's then brought the majority of the reduction in computer costs. Today the same computation would be roughly 40 million times cheaper.

Lack of programming and graphics infrastructure dominated the early years in creating the Simulation And Modeling of Profiles in Lithography and Etching (SAMPLE) program in 1975 [30, 31]. Sharad Nangonakar and later Gino Addiego working with Bill Oldham developed the common infrastructure core. This consisted of an input text parser written in Fortran, as well as save and load commands of human readable files for profiles, and line printer plots for line-edge profiles and images. The physical processes modules were developed by Mike O'Toole (image and resist development), John Reynolds (etching) and S. Cheung (deposition). Robert Jewett and Paul Hagouel developed the string and ray-trace dissolution algorithms [32]. A systematic good software practice tied the function and physics together. This included common blocks with specific categories of information, command numbers organized by process, and specific formats for code documentation and User Guide entries. Sharad Nandgonkar also made the keen observation that the

fundamental advantages of simulation over experiment are 'Controllability' and 'Observability' (which were terms borrowed from control system theory).

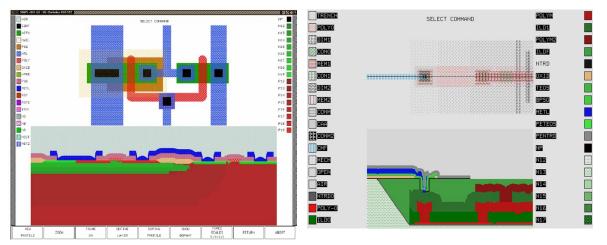

By 1982 the graphical infrastructure had improved thanks to the Tektronix color graphics terminals and the 'C' programming language. This made programs like SIMuation of Profiles from the Layout (SIMPL) were possible [33, 34]. SIMPL used a process flow and process modules with a cutline on a layout to generate a cross-section of a fabricated device. The need for automatically generating device cross-sections was the suggestion of Yoshi Sakai of Hitachi who hade developed a self-aligned CMOS twin-well process. With 'C' multiple processes could forked and this allowed any rigorous process simulator such as SAMPLE to be invoked from within SIMPL. The user could thus choose between a back-of-the-envelope geometrical model or rigorous simulation. The masks could be manipulated as well as the process flow. For example the user could introduce a worst case misalignment and view the results. Also a hunch function allowed Boolean operation on the masks and mask edges to locate layout regions where for example metal crossed over topography steps from several adjacent mask edges.

Fig. 7. SIMulation of Profiles from the layout construction of the device cross sectional geometry from a process flow and layout that invoked process modules. CMOS (left) and MEMS (Right)

In the early 1980's there was a clear need to understand many new exposure tool factors in imaging effects of 2D layout patterns. The aerial imaging simulator went through a series of very rapid changes. An initial 2D image capability was written by Phil Flanner. Kenny Toh added annular illumination, improved the numerical integration schemes and when he added aberrations the program became know as SPLAT[35]. David Newmark added a design interface [36]. Derek Lee added source/pupil maps and even windshield wiper shaped source elements for the EUV sources envisioned at that time. At Michael Yeung's suggestion Derek Lee implemented the thin-film effects of the wafer stack in the pupil so that the image could be calculated at any height inside the resist on an arbitrary film-stack[37]. Scott Hafeman converted SPLAT to C++ and implemented immersion as well as the complete 3D vector formulation developed by Michael Yeung the code as version 6.

The availability of the Thinking Machine's massively parallel computers in the late 80's motivated Roberto Guerrieri to lead our development of electromagnetic simulation using Finite-Difference Time-Domain equations on thousands of processors[38]. Each application stressed the code differently and stimulated a series of improvements for highly dispersive materials by Alfred Wong, acceleration for absorbers on planar multilayers for EUV masks by Tom Pistor, average materials for nonplanar defects by Yun-Fei Deng, and surface waves on metals (plasmons) by Dan Ceperley. Domain decomposition techniques were developed by Kostas Adam for applying thick-mask results to large layouts [39]. Fu-Chang Lo of Intel pointed out that full FDTD simulation of EUV buried defects was too slow for disposition of defects found during inspection. A fresh look by Michael Lam at the problem resulted in the development of a new ray-tracing EUV simulation approach [40].

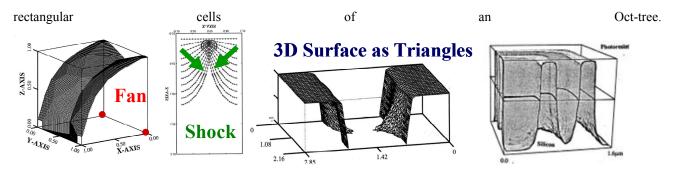

With the advent of workstations, X-windows and C++ simulation went 3D. The three-dimensional effort was based on using connected triangles to represent the surfaces while they evolved in time [41-49]. Kenny Toh wrote the resist bleaching, development, and plotting codes. Ed Scheckler developed 3D etching in NETCH. John Helmsen dealt with speeding up many of the challenging surface intersection issues using spatial decomposition of the surfaces into small

Fig. 8. Surface motion creating faceted fan in a cell model, shocks in a string model, and 3D surfaces without and with shading for lithography and pattern transfer.

Robert Wang continued the work on developing geometrical infrastructure including collaborating on standards and evaluating existing geometry engines from other fields. Robert concluded that none of the engines to date had included both surface connectivity to support visibility calculations and local spatial compartmentalization of the intersections of nearby shapes to support rapid calculations of surface collisions. Alex Wong also participated in industry wide workbench standards discussions and developed a TCAD prototype system called Process Simulation Environment (PROSE). While there was collaboration on standards a general release of an industry wide backbone TCAD system on which universities could add process models did not come to pass. Universities were unfortunately reverting back to taking time from research on new modules to reinvent infrastructure for integrating modules, task management, user interfaces and graphics.

Surface representation consisting of flat triangular patches is well suited for time-evolution of topographical profiles especially when visibility is needed. The cell, ray and string methods were compared from the start. In the cell method octagon shaped fans resulted as shown in Figure 8 unless information from distant neighbors was included. In the ray method the rays would diverge unless new rays were spawned. The string method would turn inside out at locations where two shock fronts met as shown in Figure 8. With clipping of the inverted regions and regularization of the distance between neighbors the string method worked well and for 3D it was generalized to a triangle representation. Examples of this surface representation are shown in Figure 8c and 8d without and with shading for surface reflection. For resist development the advancement algorithm was hybridized with ray tracing so that the node directions could be found with less error than occurred in estimating it with the surface normal. The 3D surface representation by triangles also had the convenience that the lines between the triangles formed ridges from which profile self-shadowing effects could be computed for deposition and etching. The surface collisions were managed using the Oct-tree.

Our 3D process simulation became unsustainable. Large software platforms are fun to prototype but a headache to make industrial grade. The problems are that codes are never bug free and new physics needs new data structures and algorithms. The prototype coding efforts are great at providing proof of concept but the documentation is thin and nearly non-existent in the code itself. Thus it is a terrible task even as a good programmer to be asked to go into another student's code and make a change. One student expressed this degree of difficulty as 'Finding a bug in another student's code is like learning Russian by proof reading War and Peace.'

A surprising breakthrough occurred in stable and fast time-evolution algorithms based on the 'level set' method introduced by James Sethian [50]. In this method the time-evolving surface is considered to be a constant height (or level) contour on a surface in an N+1 dimension space. The advantage is that the computational challenges of diverging profiles (fans) and colliding surfaces (shock fronts) are treated automatically. The unexpected result was that even with the increase in dimensionality the 'level set' method was more efficient than other methods when simulating only a narrow band around the level of interest. The rapid adaptation of this superior method by the EDA industry was another reason that our research group move on to new endeavors.

One infrastructure bright spot in 1997 was the creation of remote simulation through client-server graphical interfaces using PC's[51]. The availability of the JAVA programming language and web interfaces on PC's inspired a team of undergraduate Computer Sciences programming students. They developed Lithography Analysis using Virtual Access (LAVA) with the motto 'LAVA was hotter than JAVA.' The server web site provided the user with menu of graphical screens on their client PC and they could drag sliders, type parameters and select options. The master screen and a defect printability applet from that era are show in Figure 9. The simulation button would then collect the input data and send it

back to the server at Berkeley to run SPLAT, SAMPLE, TEMPEST or SAMPLE-3D. The graphical results were then sent back to the client with a plot. Over the next several years some 18 undergraduates generated graphical JAVA applets for specific applications ranging from education, illustrating specific phenomena, or making serious assessments of cutting-edge issues. While security protection has dampened the use of LAVA by industry it is still a great tool for students to run homework problems and for lithographers to test ideas at cuervo.eecs.berkeley.edu/Vocano

Fig. 10. Graphical interface for remote simulation. LAVA main page (left) and applet for moving a defect near a 2D feature (right).

The speed up in aerial image calculation to enable OPC also deserves special mention as major breakthroughs in algorithms were necessary to make this possible. Although our research group was aware of this new challenging opportunity we stuck with the basic physics of lithograpy. Several other groups developed entirely new formulations that were suitable for treatment of a full chip. One common element was the use of Systems of Coherent Systems (SOCS) with a few to a dozen kernels to approximate image evaluation with partial coherence[52,53]. Zone-Sampling with local functions were also introduced [54]. These OPC codes also contained notable other improvements such as the factoring rectangles into corner shapes and the pre-computation or integrals with various overlap lengths. Extension of the SOCS to include illuminatione effects was made by Socha [55]. In hindsight we may now, in part, be able to answer John Stirniman's question from the early 90's as to the possible physical explanation of the local Zone-Sampling functions. These functions are likely closely related to those found from physical principles that drove the development of Pattern Matching.

#### 6. CURRENT SIMULATION CHALLENGES

Simulation continues to face many challenges. From a historical viewpoint the biggest continuing challenge is sufficient calibration to be predictive of manufacturing. Simulation can manage the complexity of the interplay of multiple factors that is well beyond human comprehension. However, to make correct predictions the physical models must be complete and have accurate parameters. With minimal effort it is easy to predict important trends and then follow up with experiment. To make predictions accurate to a few percent in advance requires a Herculean effort. Unfortunately the important physical effects and their associated parameters are always growing. Some 25 parameters were required in the SAMPLE code in 1975. Today the required number of parameters is roughly an order of magnitude larger. This is due to the required level of specific details of the exposure tooling, resist materials, masks, OPC, set-point and their variations. This information is hard measure and often proprietary. In fact, the calibration of models and simulation appears to be an emerging frontier of competition rather than one of industry wide collaboration.

A second major challenge is modeling of chemically-Amplified Resist Systems (CARS). Given the importance of CARS it is surprising how little predictive modeling is available. This is because the deprotection process during the Post-Exposure Bake (PEB) more challenging than modeling point defects and concentration dependent diffusion in silicon. The deprotection reaction is more like an explosion than a simple chemical reaction and many tens of species are created. In addition, the state of the mechanical structure of the polymer is also undergoing change. It first becomes very porous accelerating diffusion and soon collapses to restrict diffusion. Thus it is possible for a chemically amplified resist to dynamically first have reaction enhanced and later have reaction retarded diffusion. Highly sensitive interactions also occur with the atmosphere and substrate to cause T-topping and footing. Even an acid buffering effect that interacts with base quenchers has been reported. Many of these effects can be viewed directly by making double exposures of crossed or slightly tilted (10°) features as demonstrated by Lei Yuan [26].

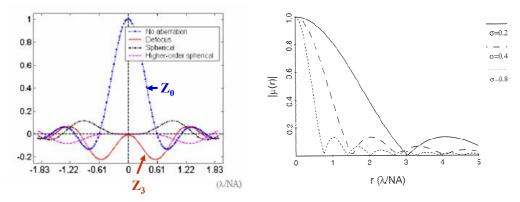

Fig. 10 Lateral influence functions for proximity (Z0) and focus (Z3) and the mutual coherence function from [56] for top-hat illumination as a function of  $\lambda$ /NA.

A third and growing major challenge with small features and off-axis illumination is what might be called Lurking Lateral Light. Co-optimization of the illumination with the mask layout provides important leverage. But there are three inherent practical problems in the image synthesis problem. First as Marc Levinson points out, light (constructive interference) cannot be made small but darkness (destructive interference) can. Remember that a single sub-resolution pixel produces a point spread function that has a diameter equivalent to  $k_1$  of 1.22 (see the curve for Z0 term in Figure 10a) and is a rather fat pencil. Thus in going below  $k_1$  of 0.35 it is basically the deep nulls that must be synthesized and used to write features. Second, the use of highly localized illumination that is highly off-axis illumination chances the lateral coherence with distance across the mask. A sinusoidal variation generally occurs and the envelope dies out only after as many as 10 feature sizes in every direction. This combining of spillover from multiple fat pencils is like adjusting individual terms in sums of large numbers to get zero only in this case multiple zero locations are needed and they must form the desired 2D device pattern. The third problem is that focus is not a small aberration and spills over light laterally into the device forming nulls. This electric field spillover is in quadrature so the extra light in the nulls grows only as the square of defocus. If the illumination, however, is not a perfectly even function of angle there will also be a quadrature component with distance across the mask with which the focus spillover can react. Thus the Lurking Lateral Light challenges low k1 manufacturing to be near perfect in mask/source optimization, mask making and illumination.

Mask edge effects are growing fourth challenge that spans both DUV and EUV. Electromagnetic studies of transmission through ATT-PSM by Marshal Miller [57] have found that the mask edges themselves produce imaginary or out of phase components on each edge as well as an effective bias toward the absorber. This is typically equivalent to a  $0.1\lambda$  (20 nm) wide strip of quadrature phase electric field of the strength of the clear field at each mask edge. Unfortunately these DUV masks edge effects are also dependent on the angles in off-axis illumination. In focus little effect is seen other that a bias. But the compounding of this effect by the Lurking Lateral Light discussed above produces a tilt of the Bossong plot and a reduction in the process window. To develop EUV many of the mask edge and defect printability characterization process will need to be revisited. The challenges are that the height of the mask absorber is multiple wavelengths and that nonplanar defects occur in the multilayer coatings and are partially buried by the mask absorber. The lower NA, refractive near unity, and surface smoothing during multilayer deposition appear to help.

#### 7. GROWTH AREAS FOR SIMULATION

In addition to the specific challenges discussed above there are additional major growth areas for the application of simulation. In some sense these are activities would be even more challenging to carry out without simulation. The most important of these is to assist in providing the Super-Glue needed to tightly couple design and fabrication. Designers need no-fault assurance tools that guarantee that the process of mapping their circuit design into silicon will result in product design that work correctly. Simulation will play many roles in this activity. First simulation can provide a rational foundation and basis for understanding design rules. Modeling and simulation can capture process characteristics in an efficient manner such that they can be applied to validate arbitrary new layouts. Simulation will enable pre-compensation in anticipation of known manufacturing nonidealities. Simulation can drive early stages of

design in Design for Manufacturing and guide manufacturing tuning in Manufacturing for Design. The lithography simulation framework will also facilitate the continued expansion of the design/process interface to other processes such as etch, stress, RTA, etc.

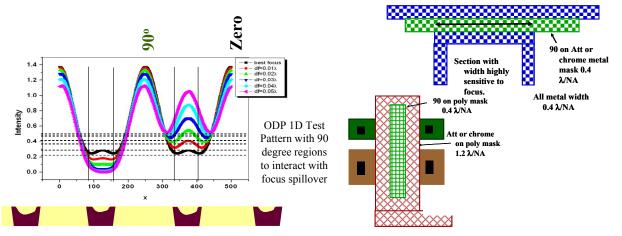

A second growth area for simulation is it's application to improve metrology and in turn synergistically calibrate simulation parameters themselves. Simulation can provide a framework for planning metrology efforts to characterize levels and sources of variation. This can be done by first estimating expected parameter change influences and their interdependencies. This information can then be used create more efficient and effective measurement and analysis strategies. A further opportunity is to create parameter specific test-patterns with enhanced sensitivities for triangulation of effects. The sensitivities of these test-patterns can be several times more sensitive as well as more parameter isolating the product itself. The best results are, however, likely through new liberties and levers such as allowing a small amount of extra mask writing to create 90° phase areas that respond interferometrically. An example of for element grating test pattern for monitoring focus with Optical Digital Profilometry is show in Figure 11 [58]. Here the spacing and phasing of the spillover is chosen to produce opposite behaviors in the two null regions.

A third growth area for simulation is electronic test circuits that automate chip self-testing. The 'white space' between design blocks is commonly used to insert test circuits including ring oscillators and counters. These circuits are activated by signals on scan chains and the measurement results are self-reported. There is even a move toward assuring that the first silicon boots a core UNIX kernel that allows the chip itself to take over and manage the electrical performance measurement process. Similarly this self-testing can even be carried out years later on field failures. Electrical testing statistics are, of course, much more directly related to what designers need to know than physical dimensions. They even reveal new sources of process variation[57]. With the advent of electronic testing, there are new opportunities to communicate with designers and create circuit layout patterns with enhanced and parameter isolating response. Solutions can be pursued across disciplines rather than within disciplines by providing collaborative frameworks to view the same information in terms of concepts for which they have an existing intuition (layout, BSIM, SPICE) [59]. Layouts that are hyper-sensitive can also be created such as the gate and interconnect layouts in Figure 12 that react to focus. [60,61].

A fourth growth area for simulation is moving the process physics up into the design process itself without burdening the designers. Information about process nonidealities is needed well before any physical layout is made, in guiding the physical layout, in decomposing it into multiple patterns or spacers, and in pre-compensating each of the individual patterns. Here the rigorous predictive simulation will be replaced by first-cut accurate fast-CAD models. These modes need to capture much of the important effects but be exercisable in many orders of magnitude shorter execution times. This field is wide open for new strategies. One strategy that we have pursued is to use Pattern Matching as discussed earlier. This might even be applied within decomposition algorithms for double patterning [62].

Fig. 12. Hyper-sensitive focus monitors based on utilizing 900 phase shifted layout elements for Optical Digital Profilometry measurement and electronic testing of gates and interconnect.

#### 8. CONCLUSION

The trigger event for lithography modeling was the creation of automated thin-film measurement equipment and its adaption to measure resist absorption and thicknesses change in situ. These measurements established the Dill model for

positive photoresist. While the feature sizes in projection printing today are far smaller than imagined, extremely sophisticated tooling, materials, enhancement techniques and sophisticated models are in use. Simulation has paid for itself by contributing to guiding technology development, assessing tool options, determining set-points, interpreting diagnostics, control, Fab calibration, OPC/PPC, Manufacturing-for-Design, and Design-for-Manufacturing.

The practice of lithography has benefitted from the use of illumination that under filled pupils creating partial coherence but this made characterization of lithography less than straight forward. As a result many of the guidelines for image quality, mask making, defect/feature interactions, mask edge effects came about only after characterization through simulation. Simulation has also made new discoveries such as Intensity Imbalance in Phase-Shifting-Masks and lead to new self-interferometric measurement techniques, new theoretical formulations for aberration effects, and new first-cut accurate fast-CAD tools for design.

It is not hard to be successful in simulation with a 40 million fold reduction in cost per CPU cycle over the last 35 years. The associated paradigm shifts in computational engines have brought about new algorithms and computational uses. The current challenges include Fab calibration, Chemically-Amplified Resist Systems, Lurking Lateral Light, and mask edge effects in DUV and EUV. Growth areas for simulation going forward include creating the glue between IC design and fabrication, synergism with metrology of variations, electronic self-testing of specific manufacturing parameters, and moving the process physics up into the design process itself without burdening the designers.

#### ACKNOWLEDGEMENT

This paper is a tribute to both to the creativity, excitement and drive of the students who made did the work and to the technologists who asked leading questions that motivated and focused these contributions.

This research project has been partly funded by the Feature Level Compensation and Control grant, a UC discovery project supported in part by the following companies: Advanced Micro Devices, Applied Materials, ASML, Cadence, Canon, Cymer, Ebara, Hitachi Global Storage Technologies, Intel, KLA-Tencor, Magma Mobility Electronics, Mentor Graphics, Nikon Research, Novellus Systems, Panoramic Technologies, Photronics, Synopsis, Tokyo Electron, Toppan Photomasks. This research was also partly funded by SRC Grant1443 and Intel.

#### REFRENCES

<sup>[1]</sup> Frederick H. Dill, The Basis for Lithographic Modeling," SPIE. Vol. 5754, pp. 377-382.

<sup>[2]</sup> Frederick H. Dill, "Optical Lithography", IEEE Trans. Electron Devices, ED-22, No. 7, pp. 440-444, 1975.

<sup>[3]</sup> F.H. Dill, W. Hornberger, P. Hauge and Jane Shaw, "Characterization of Positive Photoresists", IEEE Trans. Electron Devices, ED-22, No. 7, pp. 445-453, 1975.

<sup>[4]</sup> Karl L. Konnerth and F.H. Dill, "In-Situ measurement of Dielectric Thickness During Etching or Developing Process," IEEE Trans. Electron Devices, ED-22, No. 7, pp. 453-456, 1975.

<sup>[5]</sup> F.H. Dill, A. R. Neureuther, J.A. Tuttle and E.J. Walker, "Modeling Projection printing of Positive Photoresists," IEEE Trans. Electron Devices, ED-22, No. 7, pp. 456-464, 1975.

<sup>[6]</sup> Chris Mack, "Thirty Years of Lithography Simulation," SPIE Proc. 5754, pp. 1-12, 2004.

<sup>[7]</sup> P.D. Robertson, F.W. Wise, A.N. Nasr, A.R. Neureuther and C.H. Ting, "Proximity Effects and Influences of Nonuniform Illumination in Proceedings SPIE Conference, Optical Microlithography, Vol.34, pp.37-43, 1982.

<sup>[8]</sup> M.D. Prouty and A.R. Neureuther, "Optical Imaging with Phase Shift Masks," SPIE Vol. 470, Optical Microlithography III, pp. 228-232, March 1984.

<sup>[9]</sup> A.R. Neureuther, P. Flanner III and S. Shen, "Coherence of Defect Interactions with Features in Optical Imaging," J. Vac. Sci. Technol. B, pp. 308-312, Jan/Feb. 1987.

<sup>[10]</sup> V. Mastromarco, K.H. Toh and A.R. Neureuther, "Printability of Defects in Optical Lithography: Polarity and Critical Location Effects," J. Vac. Sci. Technol. B. pp. 224-229, Jan/Feb 1988.

<sup>[11]</sup> T. Watanabe (Intensity dip for defects of various phases through focus).

<sup>[12]</sup> Pierrat, C., Wong, A. and Vaidya, S., "Phase-shifting mask topography effects on lithographic image quality", Electron Devices Meeting, Dec 1992.

<sup>[13]</sup> R. Socha, M. Yeung, A.R. Neureuther, R. Singh, "Models for Characterizing Phase-Shift Defects in Optical Projection Printing," IEEE Transactions on Semiconductor Manufacturing, Vol. 8, No 2, pp. 139-149, 1995.

<sup>[14]</sup> R. Socha, A. Wong, M. Cagan, Z. Krivokapic, and A.R. Neureuther, "Effects of wafer topography on the formation of polysilicon gates," Proc. SPIE Vol. 2440, pp. 361-371, 1995.

<sup>[15]</sup> T.V. Pistor, K. Adam, and A. Neureuther, "Rigorous simulation of mask corner effects in EUV lithography," J. Vac. Sci. Technol. B., Vol. 16 (6), pp. 3449-3455, Nov/Dec 1998.

<sup>[16]</sup> K. Adam, S. Hotta and A.R. Neureuther, "Characterization of phase defects in phase shift masks," J. Vac. Sci. Technol. B, 18(6), pp. 3227-3231, Nov/Dec 2000.

<sup>[17]</sup> Y. Deng, T. V. Pistor, A. R. Neureuther, "Models for characterizing the printability of buried EUV defects", Proc. SPIE, Vol. 4343, pp. 551-558, 2001.

<sup>[18]</sup> Andrew R. Neureuther and Daniel Ceperley, "Modeling and Simulation for Nanometrics," J. Vac Sci. Technol., Vol. 23, pp. 2578-2583, Nov. 2005.

<sup>[19]</sup> O'Toole resist M.M. O'Toole and A.R. Neureuther, "The Influence of Partial Coherence on Projection Printing", SPIE, Vol. 174, Semiconductor Microlithography IV, Vol.174, pp.22-27, April 1979.

<sup>[20]</sup> D.J. Kim, W.G. Oldham, and A.R. Neureuther, "Development of Positive Photoresist," IEEE Trans. Elec. Dev., Vol. 31, pp. 1730-1735, December 1984.

<sup>[21]</sup> Chris A. Mack, "Inside PROLITH: A Comprehensive Guide to Optical Lithography Simulation", Finle Technologies, Inc., 1997.

<sup>[22]</sup> R.A. Ferguson, C.A. Spence, E. Reichmanis, L.F. Thompson, and A.R. Neureuther, "Investigation of the Exposure and Bake of a Positive-Acting Resist with Chemical Amplification," SPIE Proceedings, Vol. 1262, pp. 412-424, 1990.

<sup>[23]</sup> C.A. Spence, R.A. Ferguson, A.R. Neureuther and W.G. Oldham, "Characterization and Modeling of Materials for Photolithography Simulation," Solid State Electronics, Vol. 33, No. 6, pp. 625-638, 1990.

<sup>[24]</sup> M. Zuniga, G. Wallraff and A.R. Neureuther, "Reaction diffusion in deep-UV positive tone resist systems," Proc. SPIE Vol. 2438, pp. 113-124, 1995.

[25] E. Croffie, L. Yuan, M. Cheng and A. Neureuther, "Modeling influence of structural changes in photoacid generators on 193 nm single layer resist imaging," J. Vac. Sci. Technol. B, 18(6), pp. 3340-3344, Nov/Dec 2000.

[26] L. Yuan, S. Nagahara, A. R. Neureuther, "Applying double exposed sharp tip technique to characterize material

<sup>[26]</sup> L. Yuan, S. Nagahara, A. R. Neureuther, "Applying double exposed sharp tip technique to characterize material phenomena in DUV photoresist", SPIE Vol. 5753, pp. 1108-1118, May 2005. <sup>[27]</sup> Garth Robins, Konstantinos Adam, and Andrew Neureuther, "Measuring optical image aberrations with pattern and

<sup>[27]</sup> Garth Robins, Konstantinos Adam, and Andrew Neureuther, "Measuring optical image aberrations with pattern and probe based targets", J. Vac. Sci. Technol. B 20, 338 (2002) <sup>[28]</sup> G. McIntyre, J. Holwill and A. R. Neureuther, Screening layouts for high-numerical aperture and polarization

<sup>[28]</sup> G. McIntyre, J. Holwill and A. R. Neureuther, Screening layouts for high-numerical aperture and polarization effects using pattern matching, Journal of Vacuum Science & Technology B: Microelectronics and Nanometer Structures -- November 2005 – Volume 23, Issue 6, pp. 2646-2652

<sup>[29]</sup> F. Gennari and A. Neureuther, "A Pattern Matching System for Linking TCAD and EDA", IDQED 2004: 165-170.

<sup>[30]</sup> W.G. Oldham, S.N. Nandgaonkar, A.R. Neureuther, and M.M. Toole, "A General Simulator for VLSI Lithography and Etching Processes. Part I - Applications to Projection Lithography," IEEE Transactions on Electron Devices, Vol.ED-26, No.4, pp.717-722, April 1979.

<sup>[31]</sup> W.G. Oldham, A.R. Neureuther, C. Sung, J.L. Reynolds, and S.N. Nandgaonkar, "A General Simulator for VLSI Lithography and Etching Processes: Part II-Application to Deposition and Etching", IEEE on Trans. on Electron Devices, Vol.ED-27, No.8, pp.1455-1459, August, 1980.

<sup>[32]</sup> R.E. Jewett, P.I. Hagouel, A.R. Neureuther, and T. Van Duzer, "Line-Profile Resist Development Simulation Techniques", Polymer Engineering and Science, Vol.17, No.6, pp. 381-384, June 1977.

<sup>[33]</sup> M.A. Grimm, K. Lee and A.R. Neureuther, "SIMPL-1 (SIMulated Profiles from the Layout - version 1)", IEDM Technical Digest, pp. 255-258, 1983.

<sup>[34]</sup> K. Lee, Y. Sakai and A.R. Neureuther, "Topography Dependent Electrical Parameter Simulation for VLSI Design," IEEE Trans. Elec. Dev., Vol. 30, pp. 1469-1474, November 1983.

<sup>[35]</sup> K.H. Toh and A.R. Neureuther, "Identifying and Monitoring Effects of Lens Aberrations in Projection Printing," SPIE Proceedings, Vol. 772, pp. 202-209, 1987.

<sup>[36]</sup> D.M. Newmark and A.R. Neureuther, "Phase-Shifting Mask Design Tool," SPIE Vol. 604, pp. 226-235, 1991.

<sup>[37]</sup> M.S. Yeung, D. Lee, R. Lee, and A.R. Neureuther, "Extension of the Hopkins' Theory of partially Coherent Imaging to Include Thin-Film Interference Effects," SPIE Vol. 1927, pp. 452-463, 1993.

<sup>[38]</sup> J. Gamelin, R. Guerrieri, and A.R. Neureuther, "Exploration of Scattering from Topography with Massively Parallel Computers," J. Vac. Sci. Technol. B., Vol. 7, No. 6, pp. 1984-1990, Nov/Dec 1989. The SIMD machines did work well

for shot noise development. R.G. Guerrieri and A.R. Neureuther, "Simulation of Microcrack Effects in Dissolution of Positive Resist Exposed by X-Ray Lithography," IEEE Trans. CAD, pp. 755-764, July, 1988.

<sup>[39]</sup> K. Adam and A.R. Neureuther, "Methodology for accurate and rapid simulation of large arbitrary 2D layouts of advanced photomasks, Proc. SPIE 4562-118.

[40] M. Lam and A. Neureuther, "Fast simulation methods for defective EUV mask blank inspection," SPIE Vol. 5567, pp. 741-750, Dec. 2004.

[41] K.K.H. Toh, A.R. Neureuther and F.W. Scheelder, "The Discussion of the second second

<sup>[41]</sup> K.K.H. Toh, A.R. Neureuther and E.W. Scheckler, "Three-Dimensional Simulation of Optical Lithography," SPIE Vol. 1463, pp. 356-367, March, 1991.

<sup>[42]</sup> R.H. Wang, A. Gabara and A.R. Neureuther "BTU - Berkeley Topography Utilities for Linking Topography and Impurity Diffusion Simulations," NUPAD-IV Technical Digest, pp. 225-230, 1992.

<sup>[43]</sup> J.J. Helmsen, E.W. Scheckler, A.R. Neureuther and C.H. Sequin "An Efficient Loop Detection and Removal Algorithm for 3D Surface-Based Lithography Simulation," NUPAD-IV Technical Digest, pp. 3-8, 1992.

<sup>[44]</sup> A.S. Wong and A.R. Neureuther, "The Intertool Profile Interchange Format: A Technology CAD Environment Approach," IEEE Trans CAD, Vol. 10, No. 9, pp. 1157-1162, Sept, 1991.

<sup>[45]</sup> E.W. Scheckler, A.S. Wong, R.H. Wang, J.R. Camagna, A.R. Neureuther, G. Chin and R.W. Dutton, "A Utility-Based Integrated Process Simulation System," IEEE Trans. on CAD, Vol. 11, No. 7, pp. 911-920, July 1992.

<sup>[46]</sup> K.K.H. Toh, A.R. Neureuther and E.W.Scheckler, "Algorithms for Simulation of Three-Dimensional Etching," IEEE Trans. CAD, Vol. CAD-13, No 5, pp. 616-624, May 1994.

<sup>[47]</sup> A.R. Neureuther, R.H. Wang, J.J. Helmsen, J.F. Sefler, E.W. Scheckler, R. Gunturi, and Rex Winterbottom, "3-D topography simulation using surface representation and central utilities," pp. 57-76, 3-Dimensional process Simulation, Ed. J. Lorentz, Springer-Verlag, 1995.

<sup>[48]</sup> John H. Sefler and Andrew R. Neureuther, "Extracting solid conductors from a single triangulated surface representation for interconnect analysis," IEEE Trans. Semiconductor Manufacturing, Vol. 9, No. 1, pp. 82-86, Sept. 1995.

<sup>[49]</sup> A.R. Neureuther, R.H. Wang, J.J. Helmsen, J.F. Sefler, E.W. Scheckler, R. Gunturi, and Rex Winterbottom, "3-D topography simulation using surface representation and central utilities," pp. 57-76, 3-Dimensional process Simulation, Ed. J. Lorentz, Springer-Verlag, 1995.

<sup>[50]</sup> D. Adalsteinsson, and J.A. Sethian, "A Unified Level Set Approach to Etching, Deposition and Lithography I: Algorithms and Two-dimensional Simulations", J.A., J. Comp. Phys., 120, 1, pp. 128--144, 1995.

<sup>[51]</sup> C. Hsu, R. Yang, J. Cheng, P. Chien, V. Wen, A. R. Neureuther, "Lithography analysis using virtual access (LAVA) web resource," Proc. SPIE, Vol. 3334, pp. 197-201 (1998).

<sup>[52]</sup> Y. C. Pati and T. Kailath, "Phase-shifting masks for microlithography: automated design and mask requirements," J. Opt. Soc. Am. A 11, 2438-2452 (1994).

<sup>[53]</sup> N. Cobb and A. Zakhor, Proc. of SPIE Microlithography Symposium, 2197, 348 (1994). Or N. Cobb and A. Zakhor: Proc. SPIE 2440 (1995) 313.

<sup>[55]</sup> R. Socha, D. Van Den Broeke, S. Hsu, J. Fung Chen, T. Laidig, N. Corcoran, U. Hollerbach, K. E. Wampler, X. Shi and W. Conley, "Contact Hole Reticle Optimization by Using Interference Mapping Lithography (IMLTM)," Proc. SPIE 5377, 223-254 (2004).

[56] Alfred Kwok-Kit Wong, Resolution Enhancement Techniques in Optical Lithography, USA: SPIE Press, 2001.

<sup>[57]</sup> Marshal A. Miller, "Characterization and Monitoring of Edge Effects in Photomasks," SPIE BACUS 07

<sup>[58]</sup> Jing Xue, Costas Spanos, Andrew Neureuther, "Printing assessment of parameter specific phase-shift-mask patterns for scatterometry monitoring," SPIE 6922-63

<sup>[59]</sup> Gabor AH, et al, "Improving the Power-Performance of Multicore Processors Through Optimization of Lithography and Thermal Processing", SPIE, Volume 6521-18 (2007)

<sup>[60]</sup> Wojtek J. Poppe, Luigi Capodieci, Andrew Neureuther, "Platform for collaborative DFM", Proc. SPIE Vol. 6156, 61560E, Mar 2006.

<sup>[61]</sup> Lynn T. Wang, Wojtek J. Poppe, Liang-Teck Pang, Andrew Neureuther, Elad Alon, Borivoje Nikolic, "Hypersensitive parameter-identifying ring oscillators for lithography process monitoring," SPIE 6925-24

<sup>[62]</sup> Eric Chin, Andrew Neureuther, "Modeling timing across the lithographic process window," SPIE 6925-22

<sup>[63]</sup> Juliet A. Rubinstein, Andrew R. Neureuther, "Post-decomposition assessment of double-patterning layouts," SPIE 6924-23